Fabrication of a Superconducting Qubit Chip: A Detailed Process

2025-07-12

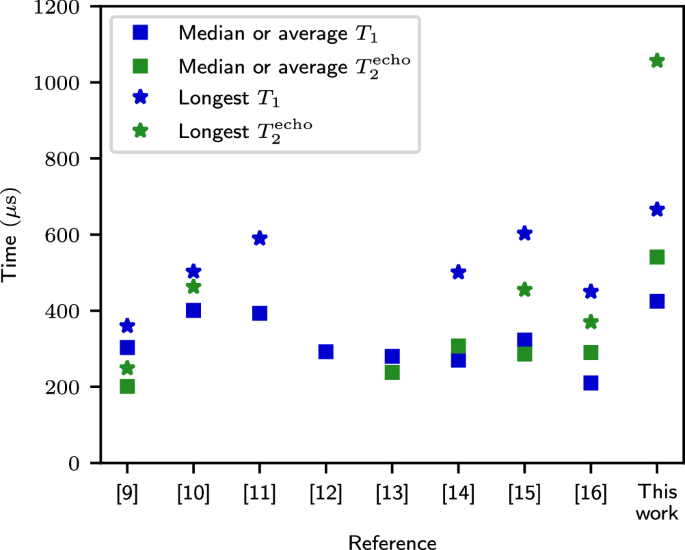

This paper details the fabrication process of a superconducting qubit chip, improving upon existing methods to enhance reproducibility. The process involves: using a 6-inch silicon wafer as substrate, sputtering a 200nm niobium film, photolithography and plasma etching to pattern the niobium, electron beam lithography to prepare Josephson junctions, aluminum deposition to form the junctions, and finally dicing and lift-off. The paper also describes the experimental setup for qubit characterization and measurement, including the cryogenic measurement system and signal processing chain. The fabricated Josephson junctions exhibited lower-than-expected critical currents, resulting in low EJ/EC ratios.