Building a CPU with Only a MOVE Instruction: A Transport Triggered Architecture (TTA) Experiment

2025-09-13

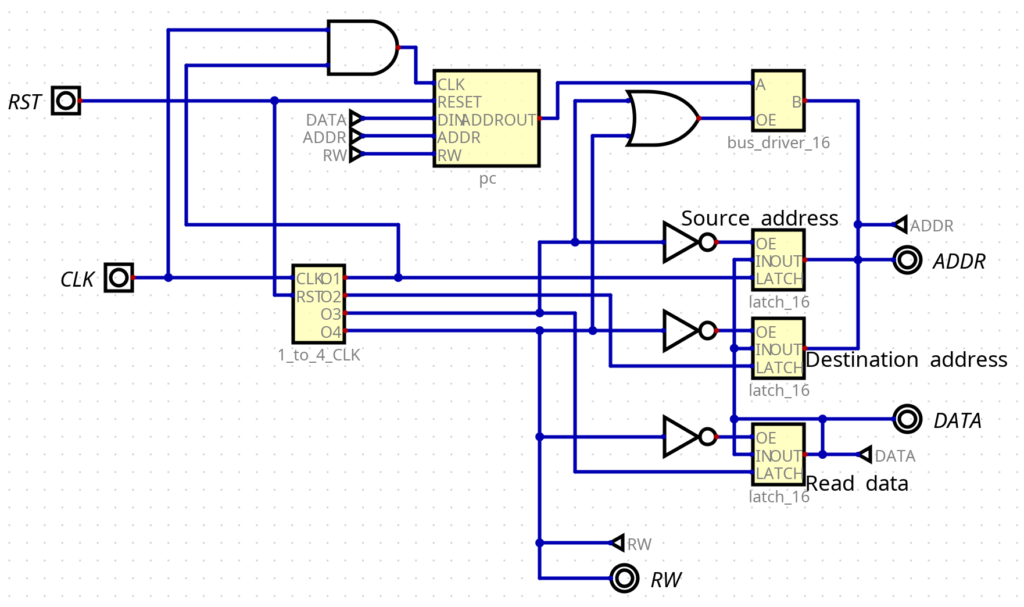

This article details the author's experience building a 16-bit CPU using only a MOVE instruction based on the Transport Triggered Architecture (TTA). Unlike traditional CPUs, TTA lacks an ALU and registers; all computations are performed in memory. Using the Digital simulator and simple logic gates and counters, the author implemented instruction fetching, data reading, and writing, successfully running a Fibonacci sequence calculation program. While TTA is not mainstream, this article showcases its simplicity and the author's deep understanding and practical skills in CPU architecture.