IBM Telum II: A Revolutionary Mainframe Processor and its Virtual Cache Strategy

2025-05-19

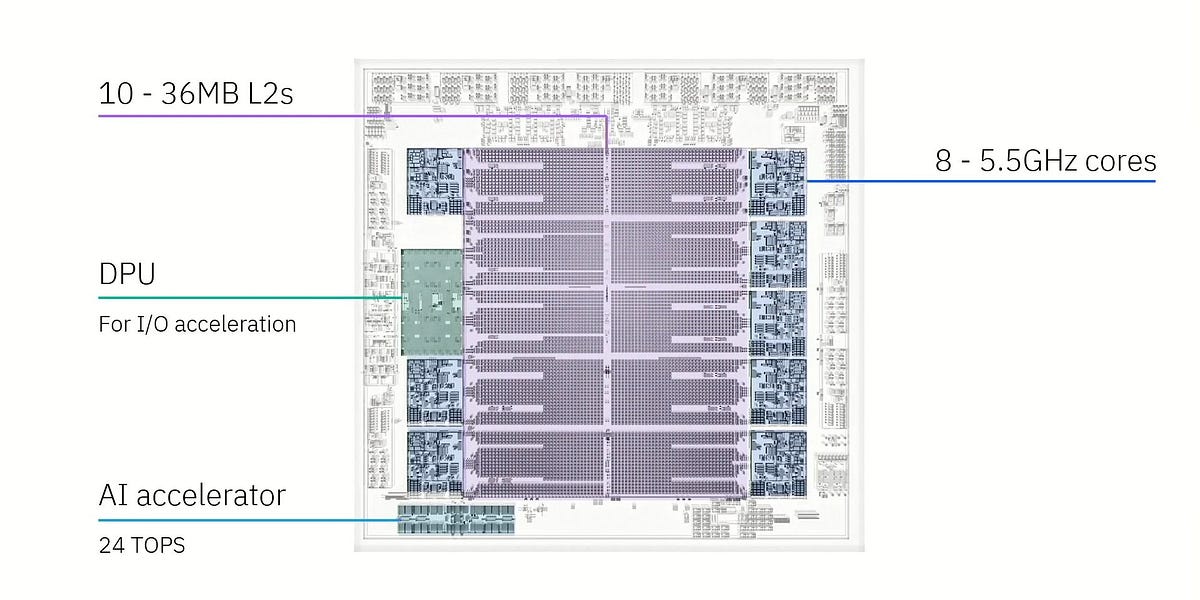

IBM's latest mainframe processor, Telum II, boasts eight 5.5GHz cores and a massive 360MB on-chip cache, along with a DPU and AI accelerator. Its most intriguing feature is its innovative virtual L3 and L4 cache strategy. By cleverly using saturation metrics and cache replacement policies, Telum II virtually combines multiple L2 caches into a huge L3 and a cross-chip L4, dramatically boosting single-threaded performance while maintaining incredibly low latency even with up to 32 processors working together. This strategy could potentially inform future client CPU designs, but challenges remain in overcoming cross-chip interconnect bandwidth limitations.

Hardware

Virtual Cache