Désactivation du cache d'opérations du Zen 5 : plongée au cœur de ses décodeurs clusterisés

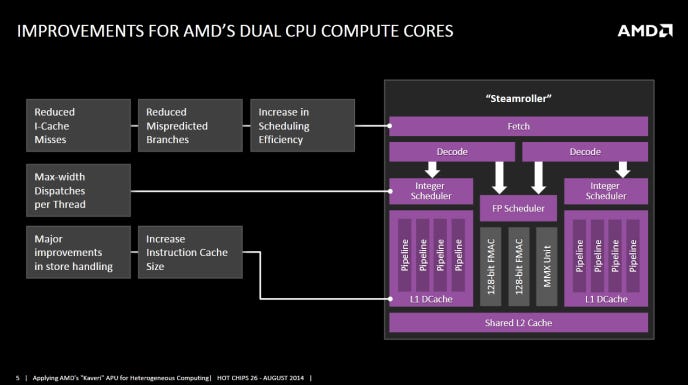

Cet article explore en profondeur le mécanisme de récupération et de décodage des instructions du processeur AMD Zen 5. Le Zen 5 utilise une architecture unique de grappes de décodeurs doubles, chaque grappe servant l'un des deux threads SMT du cœur. Normalement, le Zen 5 s'appuie sur un cache d'opérations de 6 Ko pour fournir les instructions, les décodeurs ne s'activant qu'en cas de manque de cache. L'auteur désactive le cache d'opérations, forçant les décodeurs à gérer toutes les instructions, afin d'évaluer leurs performances. Les tests révèlent des baisses de performances significatives en mode monothread avec le cache d'opérations désactivé ; cependant, en mode multithread, les grappes de décodeurs doubles compensent efficacement la perte de performances, affichant même des gains de performances dans certaines charges de travail multithread. L'auteur conclut que la conception de grappes de décodeurs doubles du Zen 5 n'est pas la source principale d'instructions, mais agit comme un mécanisme secondaire, améliorant les performances dans les scénarios à IPC élevé et multithread, complétant le cache d'opérations pour un équilibre entre performances et consommation d'énergie.