深度解析Zen 5架构:禁用操作缓存后的解码器集群表现

2025-01-24

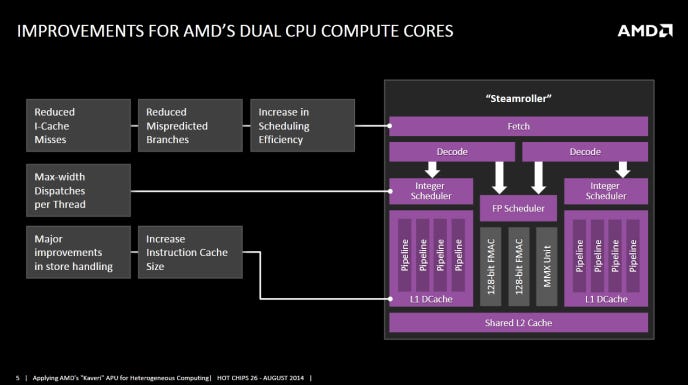

本文深入探讨了AMD Zen 5处理器的指令预取和解码机制。Zen 5采用独特的双解码器集群架构,每个集群服务于一个SMT线程。通常情况下,Zen 5依赖6KB的操作缓存来提供指令,解码器仅在缓存未命中时工作。作者通过禁用操作缓存,强制解码器处理所有指令,以此评测解码器的性能。测试结果显示,在单线程下,禁用操作缓存后性能大幅下降;但在多线程下,双解码器集群能够有效弥补性能损失,尤其在一些多线程工作负载下,甚至能取得性能提升。作者认为,Zen 5的双解码器集群设计并非主要指令来源,而是作为辅助,在高IPC和多线程场景下提升性能,与操作缓存相辅相成,实现了性能与功耗的平衡。

硬件